# FPGA based fault tolerant scheme on four switch voltage source inverter

## Ayyakrishnan.M

Department of Electrical and Electronics Engineering, St.Joseph's College of Engineering and Technology, palai, Kerala, India

| Article Info                        | ABSTRACT                                                                                                                                                      |

|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Article history:                    | This paper presents an efficient methodology to detect the fault occurrence<br>and its tolerance of four switch voltage source inverter in a single Xilinx    |

| Received Oct 12, 2015               | Spartan 3E Field Pro-grammable Gate Array (FPGA). The merit of this                                                                                           |

| Revised Nov 10, 2015                | proposed system reduces the time period between fault existence and its                                                                                       |

| Accepted Nov 26, 2015               | isolation with four switches in two legs instead of six switches in three legs<br>so as to minimize the switching losses, accuracy, and better recovery time. |

| Keyword:                            | The FPGA platform supports the run-time reconfiguration of control functions and algorithms directly in hardware and meets hard real-time                     |

| Fault tolerant control              | performance criteria in terms of timings for SVPWM generation, fault detection time and fault tolerance time. Simulation and Experimental results             |

| Four switch voltage source inverter | of this proposed system is demonstrated and verified.                                                                                                         |

| FPGA controller                     |                                                                                                                                                               |

| Space vector pulse width modulation | Copyright © 2016 Institute of Advanced Engineering and Science.<br>All rights reserved.                                                                       |

| Corresponding Author:               |                                                                                                                                                               |

| M.Ayyakrishnan,<br>Professor,       |                                                                                                                                                               |

Department of Electrical and Electronics Engineering, St.Joseph's College of Engineering and Technology, Palai. Kottayam, Kerala, India. Email: ayyakrishnan\_m@rediff.com

# 1. INTRODUCTION

Three phase voltage source inverters (VSI) are primary power components of many industrial applications like electrical machine drive, uninterruptible power system (UPS) and active power filter. VSI combined with three phase induction motor [5, 10] is used in the application of AC electrical machine drives. In the past years, three phase voltage source inverters composed of three legs with six semi-conductor devices have been used for variable speed AC motor drives [12-14, 16]. But in recent trends a new advance technology, three phase voltage source inverters with four switches [17] are very popular in the applications of power electronics. Because it consists of only a four switches in two legs and third leg is DC link capacitor [7] voltage. The cost due to less number of switches, reduction in switching losses and less chances of destroying the power switches, four switch voltage source inverters (FSVSI) are preferred over six switch voltage source inverters.

Fault is uncertainty and malfunction which leads to sudden failure or breakdown. Due to abnormal condition, a fault occurs in any system is unbelievable and it has to be isolated. To control the fault and maintain safety and reliability, the fault tolerant control (FTC) is necessary to investigate the fault occurrence and its isolation. FTC has three important schemes.

- Fault identification

- Fault isolation

- Controller scheme

In fault identification, scheme offers identification of fault , that means it investigates where the fault occurs in the processing system. Previously many papers have been published [1,4] for fault detection

methods. Investigation of the six switch voltage source pulse-width modulation (PWM) inverter system for induction motor drives on various fault modes by Kastha and Bose[3].

In fault isolation, the switching fault may be an open circuit fault or short circuit fault in the system, FTC plans and recommends an isolation process for particular fault. For example, in case of short circuit fault, isolation can be achieved by fast acting fuses.

In mathematical modeling when a fault occurs, the parameters or variables are deviated from the normal system and reaches to unstable region. Controller scheme (FTC) [3-5] is to control those variables to drive the process to maintain the desired response by designing a suitable controller. To design any system, that should be stable system and the time between fault occurrence and its isolation should be minimized so as to the system runs continuously. FTC provides a suitable controller which has to modify the parameters and the system goes to stable system. In recent years, the following controllers are used for fault tolerant schemes

- PI controlled scheme

- Fuzzy controlled scheme

- FPGA controller scheme

The above controllers are used to detect and isolate the fault which occurs in any one of the switches in the proposed inverter and also reduces or minimizes the time between the fault occurrence and its isolation. All controllers generate necessary gate pulses for triggering the power switches in FSVSI.

Recently high switching frequency power semiconductor devices such as IGBT are used for developing high frequency pulse width modulation techniques. In order to reduce the harmonics, THD, noise and better dynamic response, space vector pulse width modulation (SVPWM) is better choice for producing required gate pulses and control the output voltage. SVPWM [18] is also developing the vector durations of voltage space vectors.

Previously PI and Fuzzy control algorithms [19] were used for fault time recovery. Nowadays, FPGA controller [1,2] is used in fault tolerant scheme for better time recovery and accuracy. Many papers have been published about the fault tolerant schemes with fault detection time. Recently S.Karimi,P.Poure and S.Saadate proposed a fast power switch failure detection scheme for three phase with normal three leg voltage source inverters, in which minimization of the time interval was in the fraction of microseconds.

## 2. FAULT TOLERANT TOPOLOGY

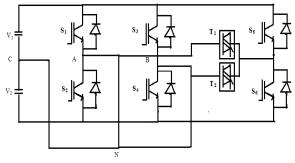

Figure 1 shows a fault tolerant topology for a four switch voltage source inverter [6-9,11] with three phase load. This proposed inverter scheme is composed of three legs with four switches ( $S_1$  to $S_4$ ) in two legs and two dc-link capacitors in third leg. In addition to that auxiliary leg (fourth leg), which is formed by two more switches ( $S_5$  and  $S_6$ ) acts as a replacing leg and two triac switches as connecting switches between inverter switching legs and auxiliary leg. When fault occurs at the any one of the switches in the inverter, the proposed system detects and isolates the faulty leg. The isolation is implemented by removing the gate signal for the particular faulty switch and triggers the corresponding bidirectional triac switch (either  $T_1$  or  $T_2$ ).

Figure 1. FSVSI fault tolerant topology

If any fault occurs at any one of the power switches in main circuit, an auxiliary leg which consists of two switches replaces that faulty leg through concerned bidirectional triac switch and the operation continues during the fault existence. For example if fault occurs in  $S_1$  or  $S_2$ , then triggering pulses given to the both switches are removed and auxiliary leg ( $S_5$  and  $S_6$ ) replaces and acts as main leg by triggering the bidirectional switch  $T_1$

According to space vector modulation analogy, components of  $\alpha\beta$  of the voltage vectors from abc voltages by clark's transformation can be written as (1)

$$\begin{bmatrix} V_{\alpha} \\ V_{\beta} \end{bmatrix} = \frac{2}{3} \begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & \frac{\sqrt{3}}{2} & -\frac{\sqrt{3}}{2} \end{bmatrix} \begin{bmatrix} V_{a} \\ V_{b} \\ V_{c} \end{bmatrix}$$

(1)

Where phase voltages are defined by (2)

$$V_{a} = \frac{1}{3} (2V_{a0} - V_{bo}), V_{b} = \frac{1}{3} (2V_{b0} - V_{a0}), V_{c} = -\frac{1}{3} (V_{a0} + V_{b0})$$

<sup>(2)</sup>

In space vector pulse width modulation, there are four possible space vectors for main circuit power switches and two vectors for auxiliary leg power switches. In four vector analogy, each voltage space vector is displaced by  $90^{\circ}$ . in  $\alpha\beta$  plane. The representation of different switching functions and space vectors shown in Table 1.

| Table 1. Switchi | ing functions a | nd Voltage vectors                            |

|------------------|-----------------|-----------------------------------------------|

| $S_1$            | $S_3$           | $V=V\alpha+jV_{\beta}$                        |

| 0                | 0               | $V_{1} = \frac{V_{dc}}{3}e^{j\frac{2\pi}{3}}$ |

| 1                | 0               | $V_2 = 2 \frac{V_{dc}}{3} e^{j\frac{\pi}{6}}$ |

| 1                | 1               | $V_{3} = \frac{V_{dc}}{3} e^{j\frac{\pi}{3}}$ |

| 0                | 1               | $V_4 = 2\frac{V_{dc}}{3}e^{j\frac{5\pi}{6}}$  |

# 3. SPACE VECTOR MODULATION AND PWM GENERATION

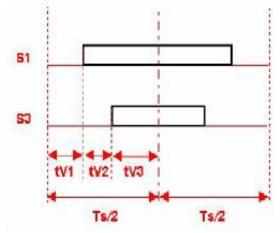

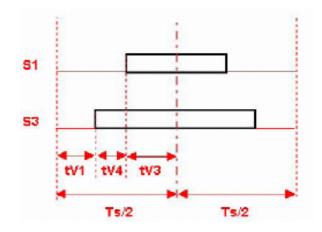

SVPWM produces necessary pulses for the switching functions  $S_1$  and  $S_3$  within the specified sampling period. During the fault conditions, there are six sectors and four voltage vectors. Switching patterns for sectors I, V, VI are shown in Figure 2. Switching patterns for sectors II, III, IV are shown in Figure 3.

## 3.1. Pulse patterns for switching in the proposed method.

According to space vector modulation

$$V * T = v_1 t_1 + v_2 t_2 + v_3 t_3 + v_4 t_4$$

(3)

After algebraic simplification time weights are

$$T = t_x + t_y + t_z$$

Voltage space vectors for each sector is given in Table.2

| Table 2. Sectors and Vectors |                                                |  |  |  |

|------------------------------|------------------------------------------------|--|--|--|

| Sector                       | Vector                                         |  |  |  |

| I,V,VI                       | $V_{1}, V_{2}, V_{3}$                          |  |  |  |

| II,III,IV                    | V <sub>1</sub> ,V <sub>3</sub> ,V <sub>4</sub> |  |  |  |

Sector I

$$t_x = t_{23f} = \frac{\sqrt{3}}{\pi} MT_s \sin(\frac{\pi}{3} - \alpha) \tag{5}$$

(4)

$$t_y = t_{3f} = \frac{\sqrt{3}}{\pi} MT_s \sin(\alpha) \tag{6}$$

$$t_z = t_{of} = T_s / 2 - t_{23f} - t_{3f} \tag{7}$$

$$t_{2m} = \frac{t_{23f}}{2} \qquad t_{3m} = \frac{t_{23f}}{2} \tag{8}$$

$$t_{3z} = \frac{t_{of}}{2}$$

;  $t_{1z} = \frac{t_{of}}{2}$  (9)

$$t_{V1} = t_{1z} \tag{10}$$

$$t_{V2} = t_{2m} \tag{11}$$

$$t_{V3} = t_{3f} + t_{3m} + t_{3z} \tag{12}$$

# Sector II

$$t_x = t_{3f} = \frac{\sqrt{3}}{\pi} MT_s \sin(\frac{\pi}{3} - \alpha) \tag{13}$$

$$t_y = t_{34f} = \frac{\sqrt{3}}{\pi} M T_s \sin(\alpha) \tag{14}$$

$$t_z = t_{of} = T_s / 2 - t_{3f} - t_{34f}$$

(15)

$$t_{3m} = \frac{t_{34f}}{2} \quad ; \quad t_{4m} = \frac{t_{34f}}{2} \tag{16}$$

$$t_{3z} = \frac{t_{of}}{2} \quad ; \quad t_{1z} = \frac{t_{of}}{2} \tag{17}$$

$$t_{V1} = t_{1z}$$

(18)

$$t_{V4} = t_{4m} \tag{19}$$

$$t_{V3} = t_{3f} + t_{3m} + t_{3z} \tag{20}$$

# Sector III

$$t_x = t_{34f} = \frac{\sqrt{3}}{\pi} MT_s \sin(\frac{\pi}{3} - \alpha) \tag{21}$$

$$t_y = t_{4lf} = \frac{\sqrt{3}}{\pi} MT_s \, \sin(a) \tag{22}$$

$$t_z = t_{of} = T_s / 2 - t_{34f} - t_{41f}$$

(23)

$$t_{3m} = \frac{t_{34f}}{2} \qquad t_{4m} = \frac{t_{34f}}{2} + \frac{t_{41f}}{2} \tag{24}$$

$$t_{lm} = \frac{t_{41f}}{2}$$

;  $t_{lz} = \frac{t_{of}}{2}$ ;  $t_{3z} = \frac{t_{of}}{2}$  (25)

$$t_{V1} = t_{1z} + t_{1m} \tag{26}$$

$$t_{V4} = t_{4m} \tag{27}$$

$$t_{V3} = t_{3m} + t_{3z} \tag{28}$$

# Sector IV

$$t_x = t_{4lf} = \frac{\sqrt{3}}{\pi} MT_s \sin(\frac{\pi}{3} - \alpha)$$

<sup>(29)</sup>

$$t_y = t_{If} = \frac{\sqrt{3}}{\pi} M T_s \sin(\alpha) \tag{30}$$

$$t_z = t_{of} = T_s / 2 - t_{4lf} - t_{lf}$$

(31)

$$t_{4m} = \frac{t_{41f}}{2} \qquad t_{1m} = \frac{t_{41f}}{2} \tag{32}$$

$$t_{3z} = \frac{t_{of}}{2} \quad ; \quad t_{1z} = \frac{t_{of}}{2} \tag{33}$$

$$t_{V1} = t_{1f} + t_{1z} + t_{1m} \tag{34}$$

$$t_{V4} = t_{4m} \tag{35}$$

$$t_{V3} = t_{3z} \tag{36}$$

# Sector V

$$t_x = t_{lf} = \frac{\sqrt{3}}{\pi} MT_s \sin(\frac{\pi}{3} - \alpha) \tag{37}$$

$$t_y = t_{12f} = \frac{\sqrt{3}}{\pi} MT_s \sin(\alpha)$$

(38)

$$t_z = t_{of} = T_s / 2 - t_{1f} - t_{12f}$$

(39)

$$t_{1m} = \frac{t_{12f}}{2} \quad ; \quad t_{2m} = \frac{t_{12f}}{2} \tag{40}$$

$$t_{3z} = \frac{t_{of}}{2} \quad ; \quad t_{1z} = \frac{t_{of}}{2} \tag{41}$$

$$t_{V1} = t_{If} + t_{1z} + t_{Im} \tag{42}$$

$$t_{V2} = t_{2m} \tag{43}$$

$$t_{V3} = t_{3z} \tag{44}$$

# Sector VI

$$t_x = t_{12f} = \frac{\sqrt{3}}{\pi} MT_s \sin(\frac{\pi}{3} - \alpha) \tag{45}$$

$$t_y = t_{23f} = \frac{\sqrt{3}}{\pi} MT_s \sin(\alpha) \tag{46}$$

$$t_z = t_{of} = T_s/2 - t_{23f} - t_{12f} \tag{47}$$

$$t_{1m} = \frac{t_{23f}}{2} \quad ; \ t_{2m} = \frac{t_{12f}}{2} + \frac{t_{23f}}{2} \quad t_{3m} = \frac{t_{23f}}{2} \tag{48}$$

$$t_{3z} = \frac{t_{of}}{2} \quad ; \quad t_{1z} = \frac{t_{of}}{2} \tag{49}$$

$$t_{V1} = t_{1z} + t_{Im} \tag{50}$$

$$t_{V2} = t_{2m} \tag{51}$$

$$t_{V3} = t_{3m} + t_{3z} \tag{52}$$

Figure 2. Pulse patterns for sectors I, V, VI

Figure 3. Pulse patterns for Sectors II, III, IV

## 4. FPGA CONTROL ALGORITHM

The Field Programmable Gate Array (FPGA) can be reprogrammed depending upon the requirement of the user. It provides instant manufacturing turnaround and negligible prototype costs which makes it suitable for embedded system design.

The sequence of steps followed when implementing PWM Generator design on FPGA. These steps are discussed in detail here.

#### 4.1. Design Entry

This is the first step of implementing a design on FPGA. In this step, the VHDL (Very High Speed Integrated Chip Hardware Description Language) code of PWM Generator Architecture was written using software Xilinx ISE 14.1.

## 4.2. RTL Simulation

The next step is RTL simulation. For this simulation VHDL Test bench was written for PWM Generator architecture and simulation was seen in Xilinx ISE Simulator.

#### 4.3. Design Synthesis

The VHDL code of PWM Generator is then synthesized using Xilinx XST and the synthesis process is used for optimizing the design architecture selected. The resulting netlist is saved to NGC file. After design synthesis, that report is generated which gives information about how many logic blocks used and what device utilization of the design architecture synthesized. It basically maps the behavioral design to gate level design.

#### 4.4. Design Implementation

In this design, there are three steps involved to implement FPGA.

- Translating

- .Mapping

- Placing and Routing

Before translating the design, User Constrained File (UCF) is written to assign pin configuration of the FPGA to the SVPWM Generator I/O"s. Translate merges together this UCF file and netlist generated after synthesis into Xilinx design file. Mapping is done to fit the design into the available resources of target device i.e. FPGA. and finally Design Implementation is Placing and Routing which places the logic blocks of the design into FPGA and route them together. So that they occupy minimum area and meet timing requirements. This operation produces NCD output file.

#### 4.5. Xilinx Device (FPGA) Programming

In this programming, the process tab of Xilinx ISE which converts the NCD file generated after routing to BIT file. It produces a bitstream for Xilinx Device (FPGA in this case) configuration. BIT file is used for programming the FPGA.

Provide a statement that what is expected, as stated in the "Introduction" chapter can ultimately result in "Results and Discussion" chapter, so there is compatibility. Moreover, it can also be added the prospect of the development of research results and application prospects of further studies into the next (based on result and discussion).

# 5. SIMULATION RESULTS

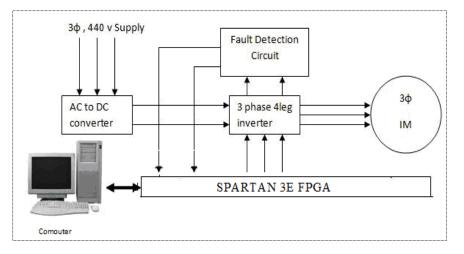

Figure 4. Experimental setup diagram for the scheme

Figure 4 shows an experimental setup for the proposed scheme. SPARTAN 3E FPGA can be used for simulating the results of triggering pulses to all power switches, line to neutral voltage waveforms and fault detection and isolation wave forms. The simulation results of SVPWM wave forms and fault detection wave form are shown in Figure 5 and Figure 6. The figure of SPARTAN 3E FPGA and device utilization is shown in Table 3 and Table 4.

| Table 3 Project status                               |                           |  |  |  |

|------------------------------------------------------|---------------------------|--|--|--|

| Fault_VSI_top Project Status (07/12/2013 - 08:45:49) |                           |  |  |  |

| Project File: Fault_tolerant_VSI.ise                 |                           |  |  |  |

| Module Name:                                         | Fault_VSI_top             |  |  |  |

| Target Device:                                       | xc7a100t-3csg324          |  |  |  |

| Product Version:                                     | ISE 14.1                  |  |  |  |

| Design Goal:                                         | Balanced                  |  |  |  |

| Design Strategy:                                     | Xilinx Default (unlocked) |  |  |  |

| Environment: System Settings                         |                           |  |  |  |

| Table 4 Device utilization                    |      |           |             |  |  |

|-----------------------------------------------|------|-----------|-------------|--|--|

| Device Utilization Summary (estimated values) |      |           |             |  |  |

| Logic Utilization                             | Used | Available | Utilization |  |  |

| Number of Slice Registers                     | 428  | 126800    | 0%          |  |  |

| Number of Slice LUTs                          | 686  | 63400     | 1%          |  |  |

| Number of fully used LUT-FF                   | 255  | 859       | 29%         |  |  |

| pairs                                         |      |           |             |  |  |

| Number of bonded IOBs                         | 13   | 210       | 6%          |  |  |

| Number of BUFG/BUFGCTRLs                      | 1    | 32        | 3%          |  |  |

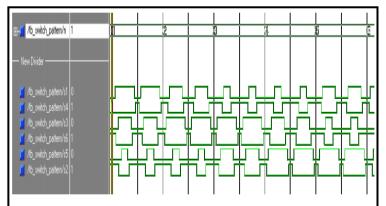

Figure 5. Simulation SVPWM wave forms of 3 ph IM

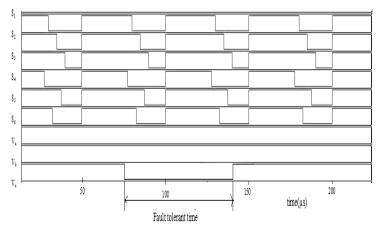

Figure 6. Simulation of pulse wave forms of six switches and fault tolerant time

# 6. EXPERIMENTAL RESULTS

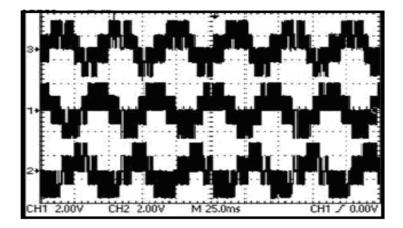

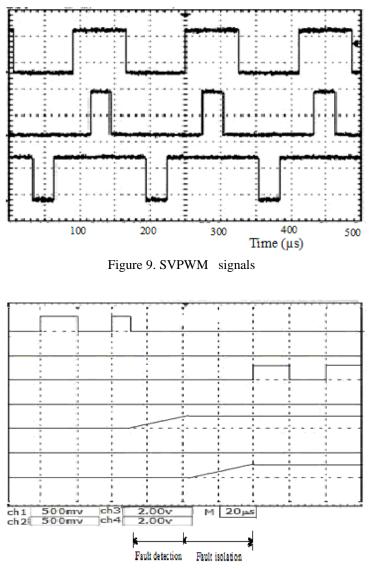

Experimental setup related to Figure 4 is shown in Figure 7. It has FPGA kit, power module and drivers and three phase induction motor. FPGA gets the values of  $V_a$ ,  $V_b$  and  $V_c$  i.e. after calculation  $V_{ref}$  for SVPWM generation. This algorithm is executed in FPGA and produces PWM signals outputs. The SVPWM signals from FPGA act as switching signals for IGBT's of VSI are represented in Figure 10. Experimental line to neutral voltages of 3 ph IM are shown in Figure 8. Observation of fault detection and isolation can be obtained from Tektronix DSO with 4 input channels as shown in Figure 10.

Figure 7. Experimental set up for FSVSI

FPGA based fault tolerant scheme on four switch voltage source inverter (Ayyakrishnan.M)

Figure 8. Experimental line to neutral voltages of 3 ph IM

Figure 10. Experimental fault detection and isolation

Figure 10 shows experimental results for 200  $\mu$ s (10 divisions, 20  $\mu$ s each) in which switching pulse for faulty leg, triggering pulse for triac switch connected to faulty switch, the fault detecting signal and the fault isolating signal are generated. First channel wave form represents triggering pulse produced by SVPWM to trigger the switch S<sub>1</sub> in which the fault is generated at 75  $\mu$ s ,Second channel represents gate pulse for Triac at which the fault is isolated by 140  $\mu$ s. Third signal represents fault detecting a signal for finding the fault detection by 25 $\mu$ s. Fourth signal represents fault isolating signal which isolates the fault by 40  $\mu$ s. So the total fault tolerant time is 65  $\mu$ s. Thus both experimental and simulation result is verified.

## 7. RESULTS AND DISCUSSIONS

FPGA based fault tolerant control on four switch voltage source inverter was investigated in both simulation and experiments through the respective software and hardware. In this scheme, first step was the implementation of fault tolerant topology of FSVSI at the time of fault existence. Next, space vector modulation was proposed to produce the necessary gate signals for the switching devices in the FSVSI. Third step was design of FPGA controller for controlling and minimizing the fault tolerant time between fault occurrence and its isolation. In the discussion of the results, the scheme was successfully conducted and the fault tolerant time was 65 µs.

In the previous research, fault tolerant topology for six switch three phase voltage source inverter was implemented and minimum tolerant time was 25 ms for PI controller based and 15 ms for Fuzzy based schemes. But in this paper, switching fault is isolated or recovered at 65  $\mu$ s. So this system is the best among the previous methods.

#### 8. CONCLUSION

This paper presents a new scheme of fault tolerant control in four switch voltage source inverter based on space vector pulse width modulation for three phase load. The proposed system uses FPGA controller which isolates the VSI power switch faults and minimizes the time interval between the fault occurrence and its isolation. The characteristics of three phase load are determined at fault conditions. Simulation results show that occurrence of faults can be effectively diagnose with minimum tolerant time. The simulation results and experimental results of the proposed system are compared and verified and it concludes the characteristics, overshoot and tolerant time of this scheme is better than six switch three phase VSI.

#### REFERENCES

- [1] S. Karimi, P. Poure, S. Saadate. Fast power switch failure detection for fault tolerant voltage source inverters using FPGA. *IET Power Electron*. 2009; 2(4): 346–354.

- [2] Giaconia G.C., Di Stefano A., Capponi G. FPGA-based concurrent watchdog for real-time control systems. *IEE Electron. Lett.* 2003; 39: 769–770.

- D.Kastha, B.K.J Bose. Investigation of fault modes of voltage-fed inverter system for induction motor drive. *IEEE Trans. Ind. Appl.* 1994; 30:1028–1038.

- [4] Peuget R., Courtine S., Rognon J. Fault detection and isolation on a PWM inverter by knowledge-based model. *IEEE Trans. Ind. Appl.* 1998; 34: 1318–1325.

- [5] Mendes A.M.S., Lopez-Fernandez X.M., Cardoso A.J.M. Thermal behavior of a three-phase induction motor fed by a fault-tolerant voltage source inverter. *IEEE Trans.Ind. Appl.* 2007; 43:724–730.

- [6] M. N. Uddin, M. A. Rahman. Fuzzy Logic controller Based cost effective four switch three phse inverter fed IPM Synchronous Motor Drive. *IEEE Transactions on industry applications*. 2006; 42(1): 21-30.

- [7] D. T. W. Liang, J. Li. Flux vector modulation strategy for a four-switch three-phase inverter for motor drive applications. *inProc. IEEE PESC*.1997; 612–617.

- [8] F. Blaabjerg, D. O. Neacsu, J. K. Pedersen. Adaptive SVM to Compensate Dc-Link VoltageRipple for Four-Switch, Three-Phase Voltage Source Inverter. *IEEE Trans. on Power electronics*. 1999; 14(4): 743-751.

- [9] F. Blaabjerg, D. O. Neacsu, J. K. Pedersen. Adaptive SVM to compen-sate DC-link voltage ripple for four-switch three-phase voltage-source inverters. *IEEE Trans. Power Electon*. 1999;14(4): 1331–1337.

- [10] R. J. Cruise, C. F. Landy, M. D. McCulloch. Evaluation of a Reduced Topology Phase- ConverterOperating a Three-phase Induction Motor. *IEEE/IEMDC Conf. Record* 1999. Seattle, USA, 1999; 466-468.

- [11] S. Takijawa, M. Tabata, T. Tanigawa, S. Igarashi, K. Kuroki. High Efficiency Drive Techniques for the Brushless DC Motor Using a Four Switch, Three-Phase Inverter. *Proceedings of IPEC 2000*. Japan, 2000; 1692-1697.

- [12] J. S. Larsen, K. Jespersen, M. R. Pedersen, F.Blaabjerg, J. K. Pedersen. Control of a Complete Digital Based Component-Minimized Single-Phase to Three-Phase AC/DC/AC Converter. *IEEE/IECON*, 1998; 618-625.

- [13] T. M. Jahns, G. B. Kliman, T. W. Neumann. Interior Permanent Magnet Synchronous Motors for Adjustable-Speed Drives. *IEEE Transactions on Industry Applications*. 1986; IA-22: 738-747.

- [14] M. Azizur Rahman, Mahinda Vilathgamuwa, M. Nasir Uddin, K. J. Tseng. Nonlinear Control of Interior Permanent Magnet Synchronous Motor. *IEEE Trans.on Ind. Applications*. 2003; 30(2): 408-416.

- [15] Matlab, Simulink User Guide, The Math Works Inc, 2003.

- [16] R. Suraj karpe. Performance of a 4-switch,3-phase inverter fed induction motor with drive system. *International Journal of Emerging Trends & Technology in Computer Science*. 2013; 2(2): 63-67.

- [17] Abolfazl Halavei Niasar, Ehsan Boloor Kashani. XMEGA Based Implementation of Four switch Three phase Voltage Source Inverter fed Induction Motor Drive. *International Journal of Power Electronics and Drive Systems*. 2013; 3(2): 218-227.

- [18] Zulkifilie Bin Ibrahim,Md. Liton Hossain, Ismadi Bin Bugis, Nik Munaji Nik Mahadi, Ahmad Shukri Abu Hasim. Simulation Investigation of SPWM THIPWM and SVPWM Techniques for Three Phase Voltage Source Inverter. International Journal of Power Electronics and Drive Systems. 2014; 4(2): 223-240.

- [19] M.Ayyarishnan, V.Maniandan. PI and Fuzzy based fault tolerant control of four switch SVPWM inverters fed induction motor. *Australian Journal of Basic and Applied Sciences*. 2014; 8(3): 188-194.

# **BIOGRAPHY OF AUTHOR**

He obtained a bachelor degree (B.E) and master's degree (M.E) from Government college of technology, Coimbatore. He got Ph.D from Annauniversity, Chennai, and Tamilnadu, India. His research area is power electronics and drives, control systems and fault tolerant control. He has 18 years of experience in teaching and 6 years in the research.