# Design and development of photovoltaic based grid interactive inverter

## G. Vijayakumar<sup>1</sup>, M. Sujith<sup>1</sup>, Dipesh. B. Pardeshi<sup>1</sup> and S. Saravanan<sup>2</sup>

<sup>1</sup>Department of Electrical Engineering, Sanjivani College of Engineering, Kopargaon, India <sup>2</sup>Department of Electrical and Electronics Engineering, Muthayanmal Engineering College, Rasipuram, India

| Article Info                                                                              | ABSTRACT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Article history:<br>Received Jul 22, 2022<br>Revised Oct 6, 2022<br>Accepted Oct 15, 2022 | In order to trail and produce the power generated on the photovoltaic (PV) array to the grid, a PV exhibit coordinated double lift DC-AC converter used as a contained single-stage micro inverter is introduced in this research. The flowing association of a DC converter, rectifier, and an inverter is used in the single-stage micro inverter to provide high supporting rise with a minimal obligation proportion. Due to the utilization of a greater variety of                                                                                                                                                                  |

| <i>Keywords:</i><br>Converter<br>Grid<br>MPPT<br>P&O<br>PV inverter                       | force-exchanging devices, the flowing association of the converters,<br>however, gives limited change efficacy. With fewer switches and hidden<br>components, the suggested disengaged double lift small inverter is intended<br>to provide high power from maximum power point tracking (MPPT)<br>proficiency, high transformation proportion, and high change effectiveness.<br>The stoop reflections and the small inverter's six distinct techniques are<br>presented. To support the display of the double lift DC-AC converter worked<br>small inverter, the recreation and results of the exploratory proto sort are<br>presented. |

|                                                                                           | This is an open access article under the <u>CC BY-SA</u> license.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

# **Corresponding Author:**

G. Vijayakumar Department of Electrical Engineering, Sanjivani College of Engineering Station Rd, opposite to Sanjivani Factory, Sanjivaani Factory, Singnapur, Kopargaon, India Email: gvijayakumarelect@sanjivani.org.in

## 1. INTRODUCTION

The use of photovoltaic (PV) power conception systems has increased concerns about the growth of a useful power shift system from the PV cluster today. By reducing the burning of non-renewable energy sources, the installation of a PV power generation system reduces CO<sub>2</sub> emissions. The PV framework provides an excellent solution for the reduction of board responsibility, power interest, and contamination. Because of their ease of maintenance, lack of emissions, and widespread accessibility, PV power producing systems are now being installed in more places. However, in the PV power framework, the output PV voltage is lower than 12 V, and a DC connection for the single-stage lattice related inverter requires a transit voltage of 325 V. Thus, the series association of PV boards is ready to provide high result voltage in the framework linked PV frameworks. However, when the shadow happens, the PV board's resultant voltage is quite low. In order to increase the result voltage of the PV framework and follow the maximum power point (MPP), an independent dc converter is used [1]–[5].

A concept for a small inverter that combines a DC assistance converter and an inverter has been presented. The flowing association of a dc converter had a major contact on the on the whole effectiveness and cost of the frameworks in the two connected PV power age frameworks [6]–[8]. There is now a better interleaved high lift DC converter that offers excellent transformation efficiency with the fewest multipliers and the lowest turns fraction of the connected inductor. To achieve high proficiency and high change percentage, a high move-forward DC converter that makes use of the capacitor multiplier and two inductors

has been introduced [9]. The reference has incorporated a flexible web-based matrix impedance regulator. estimate must focus on the inverter connected to the network's stability.

According to [10], [11] high power converter modules without a flowing transformer are introduced to eliminate the need for a matrix evade up transformer in applications that are connected to networks. The transformer galvanic detachment has fewer advantages than the transformer less network-associated PV power generation framework.

To achieve high transformation proficiency, a one stage lattice associated transformer less inverter introduced. To organize the control component between the PV show and utility lattice, a flowing staggered inverter coordinated with the PV framework has been presented in [12]. It is also expected to repay the vast array of response power [13]–[15]. To provide high supporting growth and energy change productivity, a zeta converter built with coupled inductor and capacitor multipliers for framework related PV framework has been proposed. As can be seen from the text, the single stage or three stage lattice associated inverter pulled in additional attention on the turn of events and establishment of matrix associated PV power. The rectifier and lift or buck or buck-help or cuk converter are also included. A double lift DC-AC converter-based micro inverter is therefore taken into consideration as a review in this investigation [16]. For the output voltage of the PV show, the typical single-stage micro inverter with three phase power transformation, such as DC to AC, AC to DC and DC to AC, gives substantial voltage raise. It makes use of a greater numeral of dynamic and latent plans. Therefore, when compared to the single stage supporting based small inverter, this framework's general transformation proficiency is low.

## 2. SYSTEM DESCRIPTION

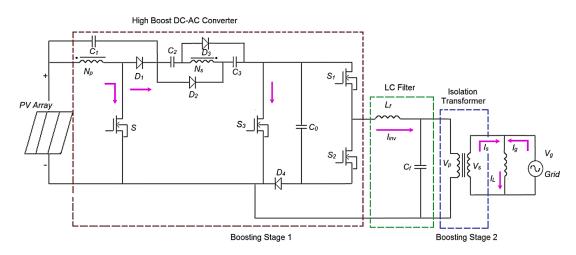

As shown in Figure 1, the planned single-phase grid associated micro-inverter is built with a dual stage DC to AC converter. A coupled inductor LP and LS, four capacitors, four diodes, and four switches comprise boosting stage 1. The main and minor windings of a boosting transformer make up the boosting stage 2. The following are the main characteristics of the proposed micro inverter: It boosts the PV array output voltage in two stages. It has one fewer active switch, one fewer diode, and two fewer capacitors than a conventional micro-inverter. It gets rid of the need for a high rate of recurrence transformer, employs simply one power conversion step, increasing system's power move capability and efficiency, and provides a tall grow to the system.

Figure 1. Dual boost converter operated as micro-inverter

## 3. WORKING PRINCIPLE

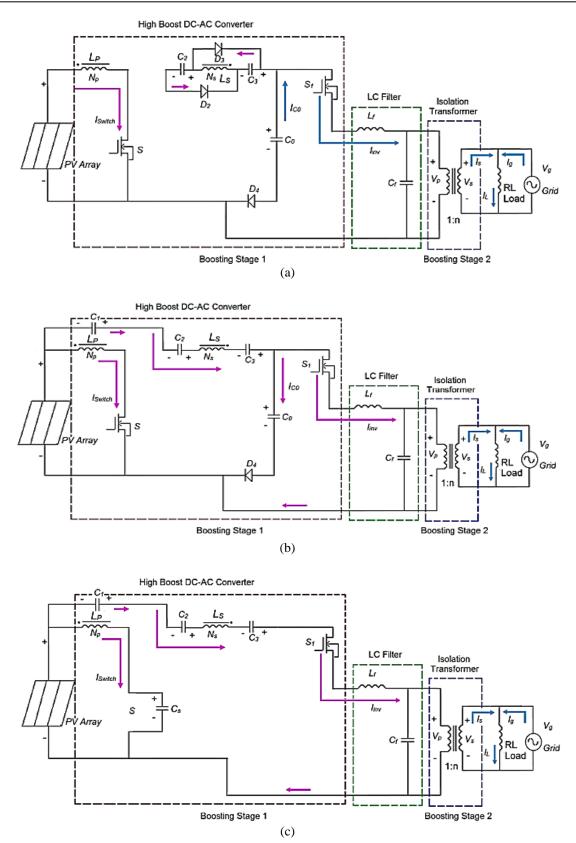

The path of the planned miniature inverter is examined below the subsequent conditions: every of the dynamic and uninvolved gadgets are excellent and without loss, The capacitors maintain a steady voltage, The current elegant through the inductor and the transformer windings are straight. The motions among the capacitance and spillage inductors are ignored, and DT is the obligation pattern of control SW, which is situate to 0.29 in regulate to continue the transformer's essential and auxiliary voltages. For optimal use of the planned miniature inverter, the DT range should be between 0.2 and 0.78. To remove the necessitate for a snubber route, the capacitor is remembered in the proposed framework between the information inductor and the altering stage. The proposed framework is implemented in six distinct modes of operation based on the

exchanging conditions of the energetic button SW, SW<sub>1</sub>, SW<sub>2</sub>, and SW<sub>3</sub>. Figure 2 depicts the various working methods of the proposed framework.

i) Mode 1 - [Time<sub>0</sub> - Time<sub>1</sub>, Figure 2(a)]

During this mode, the switch SW and SW<sub>1</sub> are "Turn ON", while the Sw<sub>2</sub> and Sw<sub>3</sub> are "Turn OFF". The voltage across the secondary of the coupled inductor  $VL_{s_1}$  forward bias the diodes  $DI_2$  and  $DI_3$  and reverse bias the diode  $DI_1$  and reverse bias the diode  $DI_1$ . The capacitor CA<sub>0</sub>, discharges the force to the main of the isolation transformer and grid during the diode  $DI_4$  and switch SW<sub>1</sub> as presented in Figure. Primary voltage of the joined Inductor  $V_{PL}$  can be written as (1).

$$V_{SPV} = V_{PL} \tag{1}$$

Where  $V_{PV}$  is the PV collection voltage from array and  $V_{PL}$  is the coupled inductor primary voltage. ii) Mode 2 - [Time<sub>1</sub> - Time<sub>2</sub>, Figure 2(b)]

In this span, the switches  $SW_2$  and  $SW_3$  are turned OFF and SW and  $SW_1$  are turned ON. The essential voltage  $V_{PL}$  and optional voltage  $V_{SL}$  of the coupled inductor forward predisposition the diode DI4 and switch inclinations the diode DI<sub>1</sub>, DI<sub>2</sub> and DI<sub>3</sub>. The power created on the PV exhibit is moved to the result capacitor CA<sub>0</sub> and framework through the switch  $SW_1$  as outlined in the Figure 2(b). The auxiliary voltage  $V_{SL}$  makes the capacitors CA<sub>1</sub>, CA<sub>2</sub> and CA<sub>3</sub> in series to release their put away energy to the capacitor C and essential of the seclusion transformer. The voltage across essential of the separation transformer  $V_{AP}$  and  $V_{oc}$  is given in (2)-(4).

$$V_{0C} \text{ or } V_{AP} = V_{SPV} + V_{CA1} + V_{CA2} + V_{S} + V_{CA3}$$

<sup>(2)</sup>

$$V_{PL} = k V_{VP} \tag{3}$$

$$V_{IL} = knV_{SPV} \tag{4}$$

Where, k is the coefficient of coupling,  $V_{OC}$  is the capacitor output voltage,  $V_{PL}$  is the coupled inductor voltage of primary the,  $V_{IL}$  is the coupled inductor secondary voltage, n is the turns ratio and  $V_{cA1}$ ,  $V_{cA2}$ ,  $V_{cA3}$  are the voltage across the capacitors CA<sub>1</sub>, CA<sub>2</sub> and CA<sub>3</sub>, respectively. iii) Method 3 - [Time2 - Time3, Figure 2(c)]

During this span, the switch SW, SW<sub>2</sub>, SW<sub>3</sub> are switched OFF and the switch SW1 is turned ON. The energy put away on the capacitors CA<sub>1</sub>, CA<sub>2</sub>, CA<sub>3</sub> and CA<sub>0</sub> are released to the essential through the switch SW<sub>1</sub>. The diodes DI<sub>1</sub>, DI<sub>2</sub>, DI<sub>3</sub> and DI<sub>4</sub> are converse one-sided by the possible diagonally the optional of the inductor coupled. The diode DI<sub>1</sub> carry out at Time=Time<sub>3</sub> and the method is end. The essential voltage of the disconnection transformer is lesser than  $V_{0C}$  as outlined in Figure 2. The auxiliary surface of the transformer supplies the positive voltage to the single-stage network. The ongoing coursed through the optional of the confinement transformer can be communicated as (5).

$$LI_{s} = \frac{1}{2N^{2}} \left( \frac{2nVl_{g}}{L_{ss}} - \frac{V_{as}}{L_{ip}} \right) t + I_{es-peak}$$

(5)

Where  $Vl_g$  voltage of grid in V,  $L_{ss}$  coupled inductor inductance and  $I_{es}$ -secondary winding peak peak current [17]–[19].

The seclusion transformer in the middle between the CL channel and framework gives the second phase of supporting ac voltage. The helping transformer (TR1) carries out two fundamental roles in the planned single-stage miniature inverter: it gives a second phase of supporting for the result voltage of dc to ac converter and it gives segregation stuck between the PV exhibit with matrix. The proposed single-stage miniature inverter works in two methods of activity in light of the framework voltage  $Vl_g$ .

i) Mode 1 [Vl<sub>g</sub>>Ve<sub>inv</sub>]: When the matrix voltage Vl<sub>g</sub> is more prominent than the Ve<sub>inv</sub>, the power shaped on the PV exhibit is moved to the lattice and burden [20]–[22]. The turns proportion or voltage proportion of the TH<sub>1</sub> is given in (6).

$$T_{kV} = \frac{V_{1g}}{V_{2p}} = \frac{2n}{1 - DT}$$

(6)

ii) Mode 2  $[V1_g < Ve_{inv}]$ : While the voltage of the grid Vl<sub>g</sub> is lesser than the Ve<sub>inv</sub>, the condenser CA<sub>1</sub>, CA<sub>2</sub> and CA<sub>3</sub> are charged through DI<sub>1</sub>, DI<sub>2</sub> and DI<sub>3</sub>. The power stored on the condenser CD<sub>0</sub> is discharged to the grid.

Figure 2. Proposed modes single-phase micro-inverter: (a) method 1, (b) method 2, and (c) method 3

Design and development of photovoltaic based grid interactive inverter (G. Vijayakumar)

298

### 4. CONTROL STRATEGIES OF THE PROPOSED SINGLE-PHASE MICRO-INVERTER

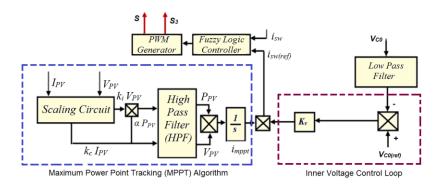

In this paper, two organize plan namely: control MPPT algorithm and control strategy Synchronizing realize to pull out the power maximum from the array PV and to grid synchronize with the planned micro-inverter.

## 4.1. Voltage control loop MPPT algorithm

In this paper, a enhance DC to AC converter operated as a single-phase voltage control loop with micro-inverter and power maximum point tracking algorithm is included to trail and control the PV power generating system. The tied inductor DC to AC converter-based tracks the power maximum point (PMP) of the PV unit. Figure 3 demonstrate the manage strategy which consists of voltage control loop and algorithm MPPT. The immediate developed power on the array PV is distribute to the grid. It is communicated in (7).

$$P_{ei} = P_{PSV} = V_{PSV} i_{siw}(t) \tag{7}$$

Where  $P_{PSV}$  is the array PV power generation and  $i_{siw}(t)$  is immediate current. The immediate switch current  $i_{siw}(t)$  is specified in (8).

$$i_{siw}(t) = \frac{P_{ei}}{V_{PV}}$$

(8)

The current reference of the SW switch is articulated as go after (9).

$$i_{siw(ref)} = k_{vt} \cdot |V_{oc}| \cdot sin(\omega t) \cdot i_{PV}$$

(9)

Where  $i_{PV}$  is the measured current from the array PV output and  $k_{vt}$  is the voltage constant. The transferred power from the array PV is depends on the assessment of  $i_{siw}$  (ref). The  $\beta P_{PV}$  is articulated as specified in (10).

$$\beta P_{PV} = k_{ii} I_{PV} \cdot k_{cs} V_{PV} \tag{10}$$

The FLC control strategy trail the power maximum and normalize the capacitor voltage. Table 1 illustrate control strategy of the fuzzy rules used. The linguistic variables are: small negative (SN), big negative (BN), zero (Zz), small positive (SP), and big positive (BP).

Figure 3. FLC based MPPT with VLL

| Table 1. Fuzzy Rules used in the | FLC |

|----------------------------------|-----|

|----------------------------------|-----|

| 1 a             | лс 1. Гu              | LLY K | uics i | iscu i | n uic | FLC |

|-----------------|-----------------------|-------|--------|--------|-------|-----|

| i <sub>sw</sub> | /i <sub>sw(ref)</sub> | BN    | SN     | Zz     | SP    | BP  |

|                 | BN                    | SN    | Zz     | Zz     | PS    | PB  |

|                 | SN                    | Zz    | Zz     | PS     | PB    | PB  |

|                 | Zz                    | BP    | SP     | Zz     | SN    | BN  |

|                 | SP                    | SN    | SN     | Zz     | Zz    | SP  |

|                 | BP                    | BN    | BN     | SN     | Zz    | SP  |

|                 |                       |       |        |        |       |     |

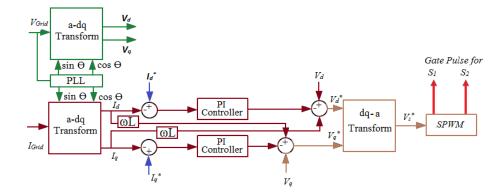

#### 4.2. Grid control strategy

The coupled inductor based double lift DC to AC inverter worked as a miniature inverter moves the control created array PV exhibit to load and matrix. It necessitates a manage unit to synchronize the converter

yield voltage with matrix. In the propose miniature inverter, the reference frame hypothesis has been executed to play out the harmonization with the network power. The organize technique comprises of DQ change, phase locked loop (PLL), PI checker, pulse width modulation with sinusoidal and DQ change is displayed in figure. The matrix boundaries  $V_{bg}$  and  $I_{bg}$  are changed over into D and Q parts by the DQ change. The p and q boundaries of the change give the insights concerning the stage point and adequacy of the matrix current and voltage, individually. The obtained faults from the equations are independently development by the two controllers PI as exposed in Figure 4.

$$I_{ed(error)} = I_{ed}^* - I_{ed} \tag{11}$$

$$I_{eq(error)} = I_{eq}^* - I_{eq} \tag{12}$$

The error practice signals are employed to create the necessary pulse for the gate of PWM inverter. The pulses gate creates by the sinusoidal PWM pulse generator controls magnitude of the inverter output voltage and the phase angle.

Figure 4. Single-phase grid synchronization with output voltage inverter

#### 5. SIMULATED RESULTS AND DISCUSSION

The reproduced form of the planned dc to ac inverter took care of miniature inverter is examined under the two different contextual investigations: case 1 is executed under the changeable sun-based irradiance and steady burden and case 2 is directed under consistent sun-oriented light with variable burden. The equal association of ten quantities of 100 W, 12 V PV board comprising of  $(12 \times 6)$  72 cells.

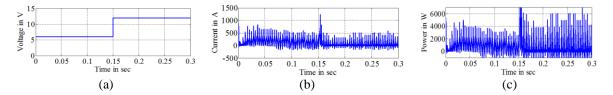

## 5.1. Case 1: Under constant load with variable solar irradiation

During this examination, the heap on the framework is kept steady and the variable sun powered illumination on the PV exhibit is considered for the investigation. The light applied on the PV cluster is expanded from 1000 W/m<sup>2</sup> to 500 W/m<sup>2</sup>. Thus, the voltage created in the PV board increments to 6 V from 12 V as shown in Figure 5(a). The PV cluster yield voltage, current and power are displayed in Figure 5(a)-Figure 5(c), individually.

Figure 5. PV array: (a) output voltage, (b) current, and (c) power under variable solar irradiance

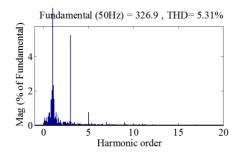

From the investigation of the mimicked results got during the variable sun-based light, it is seen that the proposed single-stage miniature inverter concentrates and moves the power delivered on the PV exhibit to load and framework with diminished quantities of dynamic control and latent components. From the Figure 6, it is seen that the planned regulators keep a consistent voltage diagonally the heap while the sunlight-based illumination modify with time. The content THD of the matrix voltage following the interconnection of the single-miniature inverter is 5.223%.

Figure 6. Voltage and current of the isolation transformer and grid

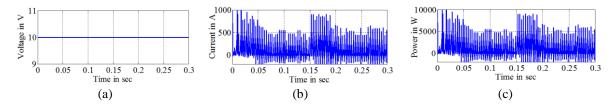

## 5.2. Case 2: Variable load with constant solar irradiation

For the duration of this examination, a changeable burden is applied to the recreated representation. A steady sun-oriented light of 810 W/m<sup>2</sup> is applied during 0 sec to 0.29 sec. The PV cluster produces 9.9 V during the whole time of examination. The PV exhibit yield voltage, current and power are introduced in Figures 7(a)-7(c), individually.

Figure 7. Array PV under constant solar irradiation (a) voltage, (b) current, and (c) power

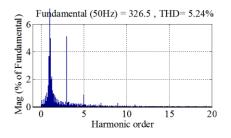

From the assessment of case 2, it is tracked down that the powerful burden on the planned miniature converter not impacted the result voltage of the miniature inverter. Figure 8 illustrate that the DC to AC inverter the result of the array PV offers high voltage gain. Figure 8 demonstrates that the interconnection of the miniature inverter is 5.224% content THD of the voltage.

Figure 8. Voltage and current of the isolation transformer and grid

# 6. EXPERIMENTAL VERIFICATION

The trial test of the planned single stage miniature inverter is achieved with one kilo volt ampere representation to check the possibility of the planned framework tentatively. The FPGA Spartan 3A regulator is used to execute the planned manages calculation. The organize calculation of the miniature inverter creates the necessary heartbeat for the synchronization of the miniature inverter with framework. The trial and error are finished by thinking about the line voltage and recurrence as 230 V and 50 Hz, separately.

The investigational model is completed for validating of the planned scheme under changeable solar irritation and active load conditions. Figure 9 illustrate the array PV voltage, across the voltage of capacitor  $CA_0$ , the primary of the voltage across transformer, current of the isolation transformer current and secondary voltage, content THD of the grid voltage after interconnection of micro-inverter.

Figure 9. Investigational outcome of the planned micro inverter under variable solar irradiation

The investigational outcome has proved that the planned scheme is competent of transferring the generated power on the array PV to load. It is also experiential that the planned scheme offers high conversion ratio for the array PV output voltage with condensed number of lively and inactive components. The mathematical correlations between the concentrated-on miniature inverter and traditional miniature inverter are introduced to show the exhibition of the proposed framework under various sun powered lights. The appraisal is centered around the quantity of dynamic switches, number of uninvolved components, AC load voltage THD content, productivity and utilization of number of diodes. The connection between the regular and proposed miniature inverter under the machine of five distinct sun-based illuminations are introduced in Table 2.

From the mathematical correlation, it is seen that the proposed miniature inverter offers high productivity and supporting addition under various sun-based illumination. The customary disconnected double lift miniature inverter requires a greater number of latent and dynamic gadgets than the concentrated-on DC-AC converter based miniature inverter.

| • 4 | assessment          | among studied and e    | onventional single phase intero-   |  |  |  |  |  |  |  |  |

|-----|---------------------|------------------------|------------------------------------|--|--|--|--|--|--|--|--|

|     | Details             | Micro-inverter studied | Boost converter fed Micro-inverter |  |  |  |  |  |  |  |  |

|     | MOSFET              | 04                     | 07                                 |  |  |  |  |  |  |  |  |

|     | Diodes              | 03                     | 05                                 |  |  |  |  |  |  |  |  |

|     | Capacitors          | 05                     | 07                                 |  |  |  |  |  |  |  |  |

|     | AC Grid Voltage THD |                        |                                    |  |  |  |  |  |  |  |  |

|     | $P_{PV} = 100\%$    | 5.29%                  | 1.24%                              |  |  |  |  |  |  |  |  |

|     | $P_{PV} = 50\%$     | 5.11%                  | 1.29%                              |  |  |  |  |  |  |  |  |

|     | $P_{PV}\!\!=75\%$   | 5.22%                  | 1.22%                              |  |  |  |  |  |  |  |  |

|     | Efficiency          |                        |                                    |  |  |  |  |  |  |  |  |

|     | $P_{PV} = 75\%$     | 92.01%                 | 88.90%                             |  |  |  |  |  |  |  |  |

|     | $P_{PV} = 50\%$     | 91.10%                 | 88.18%                             |  |  |  |  |  |  |  |  |

|     | $P_{PV} = 100\%$    | 92.92%                 | 89.20%                             |  |  |  |  |  |  |  |  |

| _   | $P_{PV} = 25\%$     | 92.50%                 | 89.05%                             |  |  |  |  |  |  |  |  |

| Table 2. | Asses | sment | among | studied | and | conven | tional | singl | e pl | hase | micro | -inverter |

|----------|-------|-------|-------|---------|-----|--------|--------|-------|------|------|-------|-----------|

|          |       |       |       |         |     |        |        |       |      |      |       |           |

#### 7. CONCLUSION

This paper concentrated on a solitary stage miniature inverter in light of double lift DC-AC converter which enjoys various benefits when implanted in photovoltaic power age framework. The proposed single-stage miniature inverter utilizes the smaller number of dynamic and detached switches than the

customary miniature inverters introduced in the writing. The framework with double stage helping works appropriately much under the low insolation conditions and guarantees ideal power move between the PV cluster and network. It improves the ability, MPPT following productivity, change effectiveness of the general framework and unwavering quality of the matrix. The elements, different working modes and plan of the proposed miniature inverter have been examined and checked by the reenactment and exploratory outcomes. From the reenacted results, it apparent that the proposed miniature inverter offers high transformation productivity around 92.88%.

#### REFERENCES

- L. S. Czarnecki and P. M. Haley, "Unbalanced Power in Four-Wire Systems and Its Reactive Compensation," *IEEE Transactions on Power Delivery*, vol. 30, no. 1, pp. 53-63, 2015, doi: 10.1109/TPWRD.2014.2314599.

- [2] K. Srinivas and S. S. T. Ram, "Three level hysteresis control of 3-phase, 4-wire shunt active power filter for harmonic compensation under unbalanced non stiff source,"*International Conference on Smart Electric Grid (ISEG)*, Sep. 2014, pp. 1-8. doi: 10.1109/ISEG.2014.7005389.

- [3] F. Nejabatkhah, Y. Li, and B. Wu, "Control Strategies of Three-Phase Distributed Generation Inverters for Grid Unbalanced Voltage Compensation," *IEEE Transactions on Power Electronics*, pp. 1-1, 2015, doi: 10.1109/TPEL.2015.2479601.

- [4] A. K. Panda and N. Patnaik, "Management of reactive power sharing & amp; power quality improvement with SRF-PAC based UPQC under unbalanced source voltage condition," *International Journal of Electrical Power & Energy Systems*, vol. 84, pp. 182-194, 2017, doi: 10.1016/j.ijepes.2016.05.010.

- [5] S. Y. Mosazadeh, S. H. Fathi, M. Hajizadeh, and A. R. Sheykholeslami, "Adaptive hysteresis band controlled grid connected PV system with active filter function,"*International Conference on Power Engineering and Renewable Energy (ICPERE)*, 2012, pp. 1–6. doi: 10.1109/ICPERE.2012.6287253.

- [6] G.-Y. Jeong, T.-J. Park, and B.-H. Kwon, "Line-voltage-sensorless active power filter for reactive power compensation," *IEE Proceedings Electric Power Applications*, vol. 147, no. 5, pp. 385-390, 2000, doi: 10.1049/ip-epa:20000541.

- [7] A. J. Viji and T. A. A. Victoire, "Enhanced PLL based SRF control method for UPQC with fault protection under unbalanced load conditions," *International Journal of Electrical Power & Energy Systems*, vol. 58, pp. 319-328, 2014, doi: 10.1016/j.ijepes.2014.01.039.

- [8] S. Y. Mousazadeh, M. Savaghebi, A. Beirami, A. Jalilian, J. M. Guerrero, and C. Li, "Control of a multi-functional inverter for grid integration of PV and battery energy storage system," *IEEE 10th International Symposium on Diagnostics for Electrical Machines, Power Electronics and Drives (SDEMPED)*, 2015, pp. 474-480. doi: 10.1109/DEMPED.2015.7303732.

- B. M. Han and B. Bae, "Unified power quality conditioner with super-capacitor for energy storage," *European Transactions on Electrical Power*, vol. 18, no. 4, pp. 327-343, 2008, doi: 10.1002/etep.178.

- [10] P. E. Melin, J. R. Espinoza, C. R. Baier, J. I. Guzman, and E. E. Espinosa, "Unified Power Quality Conditioner based on current source converters for harmonic mitigation using a decoupled control strategy," *IECON 2011 - 37th Annual Conference of the IEEE Industrial Electronics Society*, 2011, pp. 4152-4157. doi: 10.1109/IECON.2011.6119992.

- [11] D. Sreenivasarao, P. Agarwal, and B. Das, "A T-connected transformer based hybrid D-STATCOM for three-phase, four-wire systems,"*International Journal of Electrical Power & Energy Systems*, vol. 44, no. 1, pp. 964-970,2013, doi: 10.1016/j.ijepes.2012.08.019.

- [12] A. R. Reisi, M. H. Moradi, and H. Showkati, "Combined photovoltaic and unified power quality controller to improve power quality," *Solar Energy*, vol. 88, pp. 154-162, 2013, doi: 10.1016/j.solener.2012.11.024.

- [13] P. Suresh and G. Vijayakumar, "Shunt Active Power Filter with Solar Photovoltaic System for Long-Term Harmonic Mitigation," *Journal of Circuits, Systems and Computers*, vol. 29, no. 05, p. 2050081, 2020, doi: 10.1142/S0218126620500814.

- [14] N. Patnaik and A. K. Panda, "Performance analysis of a 3 phase 4 wire UPQC system based on PAC based SRF controller with real time digital simulation," *International Journal of Electrical Power & Energy Systems*, vol. 74, pp. 212-221, 2016, doi: 10.1016/j.ijepes.2015.07.027.

- [15] S. Charles and G. Bhuvaneswari, "Comparison of Three Phase Shunt Active Power Filter Algorithms," International Journal of Computer and Electrical Engineering, pp. 175–180, 2010, doi: 10.7763/IJCEE.2010.V2.132.

- [16] P. Karuppusamy, G. Vijayakumar, and S. Sathishkumar, "Certain Investigation on Multilevel Inverters for Photovoltaic Grid Connected System," *Journal of Circuits, Systems and Computers*, vol. 25, no. 09, p. 1650108, 2016, doi: 10.1142/S0218126616501085.

- [17] G. Vijayakumar and R. Anita, "Renewable Energy Interfaced Shunt Active Filter For Power Quality Enhancement Using T-Connected Transformer," UPB Scientific Bulletin Series C: Electrical engineering, vol. 76, no. 4, pp. 119–134, 2014.

- [18] D. V. P. Shimoda, F. K. A. Lima, C. G. C. Branco, R. P. Torrico-Bascope, and L. J. Camurca, "Single phase UPS with FACTS capabilities by using p-q Theory,"*IECON 2012 - 38th Annual Conference on IEEE Industrial Electronics Society*, Oct. 2012, pp. 751–756. doi: 10.1109/IECON.2012.6388657.

- [19] M. Fallah, M. Imani, H. M. Kojabadi, M. Abarzadeh, M. T. Bina, and L. Chang, "Novel structure for unbalance, reactive power and harmonic compensation based on VFF-RLS and SOGI-FLL in three phase four wire power system," 2015 IEEE Energy Conversion Congress and Exposition (ECCE), Sep. 2015, pp. 6254–6260. doi: 10.1109/ECCE.2015.7310537.

- [20] P. Kumar, N. Kumar, and A. K. Akella, "Comparative analysis of voltage and current source inverter based DSTATCOM systems," *Turkish Journal Of Electrical Engineering & Computer Sciences*, vol. 24, pp. 3838-3851, 2016, doi: 10.3906/elk-1412-32.

- [21] B. Singh, S. S. Murthy, R. S. Reddy, and P. Arora, "Implementation of modified current synchronous detection method for voltage control of self-excited induction generator," *IET Power Electronics*, vol. 8, no. 7, pp. 1146-1155,2015, doi: 10.1049/ietpel.2014.0718.

- [22] H. K. Yada and M. S. R. Murthy, "A new topology and control strategy for extraction of reference current using single phase SOGI-PLL for three-phase four-wire Shunt Active Power Filter," 2014 IEEE International Conference on Power Electronics, Drives and Energy Systems (PEDES), Dec. 2014, pp. 1–6. doi: 10.1109/PEDES.2014.7042087.

# **BIOGRAPHIES OF AUTHORS**

G. Vijayakumar 💿 🔀 🖾 🗘 is currently a Professor in the Department of Electrical Engineering at Sanjivani college of Engineering, Kopargaon, Maharashtra 423 603, India. He has totally 18 years of experience in teaching (till July 2022). He received his doctorate in Electrical Engineering from Anna University, Chennai, Tamilnadu, India in November 2014. He has been guiding 9 Ph.D., research scholars and has guided 04 post graduate projects and 11 undergraduate projects. His research concentrated on the behavior of the Shunt active filter during harmonic compensation and energy conservation. He has published over 35 articles in the peer-reviewed National & International journals, and over 23 conference proceedings, and has delivered over 08 guest lecturers in the other college programs. His h-index of 09 (Total citations 172, Source-Google Scholar) strongly endorses his high research productivity. His research interests include Power quality, shunt/series active filter, hybrid renewable energy sources, intelligent controllers. Currently, he is a reviewer for Journal of the Institution of Engineers (India): series B- springer, Asian journal of control, journal of power electronics and Journal of Circuits, Systems & Computers. He organized 08 programs and attended 39 (Seminar/Workshop/Value added courses). He has acted as the chairperson of an international conference. He taught Electrical engineering students at undergraduate and postgraduate level, over his experience. He produced 100 % results in many courses. He has the well-known professional experiences on board of studies, research and development activity, project coordination, Exam coordination, class advisor, NBA activity and technical training coordination to the students. He can be contacted at email: gvijayakumarelect@sanjivani.org.in.

**M. Sujith (D) (S) (C)** is currently working as Assistant Professor in the Department of Electrical Engineering, Sanjivani College of Engineering, Kopargaon, Maharashtra, India. He has totally 11 years of experience in teaching and received his doctoral degree from Anna University, Chennai. His main research interests include power electronic converters, compensators, power quality issues, and active power filters. He has published over 25 articles in the peer-reviewed National & International journals, and over 12 conference proceedings. He can be contacted at email: msujitheee@yahoo.co.in.

**Dipesh B. Pardeshi D X C** received Bachelor degree in Electrical Engineering from Government College of Engineering, Karad and M.E. from Government College of Engineering, Aurangabad and successfully completed Ph.D. in 2021. He is an Associate Professor and Head of Department of Electrical Engineering at Sanjivani College of Engineering, Kopargaon, Maharashtra, India, having 21 years of vast experience. His research interests include renewable energy, electrical machine, power system and power system problems. He is a Fellow of IE (India), Life Member of ISTE (India), member of IEEE and also Chartered Engineer of IE (India). He can be contacted at email: hodelecoe@sanjivani.org.in or pardeshidipeshetc@sanjivani.org.in.

**Dr. S. Saravanan b** SI **s c** is currently working as Professor in the Department of Electrical and Electronics Engineering, Muthayammal Engineering College, Rasipuram, Tamilnadu, India. He has totally 22 years of experience in teaching and received his doctoral degree from Anna University, Chennai. His main research interests include VLSI design, Appled electronics, power electronic converters, compensators, power quality issues, and active power filters. He has published over 58 articles in the peer-reviewed National & International journals, and over 26 conference proceedings. He can be contacted at email: rajaapece@gmail.com.