# Analysis and simulation of 7-level and 9-level cascaded H-bridge multi-level inverters

Sujatha Banka<sup>1</sup>, Chava Sunil Kumar<sup>1</sup>, Surender Reddy Salkuti<sup>2</sup>, Sai Sruthi Bhupathiraju<sup>1</sup>, Kasoju Pragathi Balakishan<sup>1</sup>, Paipoti Pooja Chaturya<sup>1</sup>, Rishitha Namineni<sup>1</sup>

<sup>1</sup>Department of Electrical and Electronics Engineering, BVRIT HYDERABAD College of Engineering for Women, Hyderabad, India <sup>2</sup>Department of Railroad and Electrical Engineering, Woosong University, Daejeon, Republic of Korea

#### **Article Info**

# Article history:

Received Feb 9, 2024 Revised Jul 27, 2024 Accepted Aug 15, 2024

## Keywords:

LC filter

Multi-carrier pulse width

modulation

Multi-level inverter

Pulse width modulation

Total harmonic distortion

# **ABSTRACT**

Multi-level inverters (MLIs) have created a new revolution in high-power and medium-voltage applications in industry and research. In recent years, cascaded multi-level inverters have gained significant interest due to their ability to generate high-quality output waveforms with reduced total harmonic distortion (THD). This paper discusses the analysis and simulation of 7-level and 9-level cascaded H-bridge multi-level inverters using mathematical models and simulation tools. The proposed research puts emphasis on evaluating the performance and control strategies of these inverters. The control strategies, including pulse width modulation (PWM) techniques, are discussed in depth, with a focus on their effect on output waveform quality and reduction of THD. The simulation results are compared to showcase the advantages offered by the cascaded multi-level inverters in terms of waveform quality. The findings demonstrate the superior performance and power quality advantages offered by these multilevel inverters compared to traditional two-level inverters. Additionally, a passive LC filter is designed and implemented along with a multi-level inverter configuration that helps to keep the THD within the limits specified by IEEE standards.

This is an open-access article under the CC BY-SA license.

11

# Corresponding Author:

Surender Reddy Salkuti Department of Railroad and Electrical Engineering, Woosong University Jayang-Dong, Dong-Gu, Daejeon-34606, Republic of Korea

Email: surender@wsu.ac.kr

# 1. INTRODUCTION

The increasing adoption of cascaded H-bridge multi-level inverters in recent decades is largely driven by their capacity to generate high-quality voltage waveforms with lower harmonic content. These advanced power electronics are used in electric vehicles, industrial drives, and renewable energy systems [1]. The rising demand for efficient and reliable power conversion systems has led to a growing interest in the advancement of sophisticated inverter topologies. The fundamental principle behind the cascaded H-bridge multilevel inverter (CHBMLI) lies in its capability to produce a stepped waveform by integrating the outputs of numerous series-connected H-bridge switches. The voltage levels in each H-bridge switch are typically established using a mix of DC sources, including batteries or capacitors, combined with the switching function of semiconductor devices like IGBTs and MOSFETs [2]. Modularity and scalability of the CHBMLI make it suitable for various applications where high-quality power conversion is required. The multi-level nature of these inverters allows for the production of near-sinusoidal voltage waveforms with fewer harmonics than traditional inverters. This paper contains simulation and analysis of 7-level and 9-level configurations of cascaded H-bridge inverters. In cases of switch failure or faults, the system's remaining

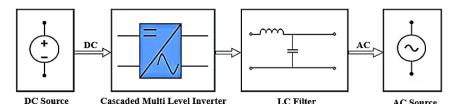

switches can continue to operate, thereby minimizing downtime and improving overall system reliability. As research and development in this field advance, these inverters are projected to be crucial in the future of sustainable energy systems and electrification [3]-[5]. Figure 1 shows the schematic diagram of the proposed model. The inverter's output voltage waveforms exhibit significant total harmonic distortion (THD). To mitigate voltage harmonics in the waveform, it is crucial to use an LC filter for suppression.

Figure 1. Block diagram of the proposed model

#### 2. COMPREHENSIVE THEORETICAL BASIS

## 2.1. Conventional inverters

The role of a power inverter is critical in converting direct current (DC) to alternating current (AC), allowing it to power a variety of devices and appliances. Static inverters that use only electronic circuitry are available, depending on application needs and technology. This breakthrough has made inverters more reliable and efficient, making them essential to many power systems and electrical equipment [6].

## 2.1.1. Two-level inverters

A two-level inverter generates two voltage levels for a load, producing  $+V_{DC}$  and  $-V_{DC}$  output voltages. The pulse width modulation (PWM) technique is used to switch between these voltage levels, generating AC voltage. However, this method has drawbacks, such as harmonic distortions and high voltage change rate (dv/dt) compared to multi-level inverters [7]. Despite the limitations, the two-level inverter is widely used in applications where output voltage distortion and dv/dt are not critical factors [8].

# 2.2. Multi-level inverters

High-performance, medium-voltage industrial applications favor multi-level inverters. They convert DC electricity from batteries, supercapacitors, or solar panels into AC power at different voltages. Multi-level inverters convert and use medium-voltage power efficiently by producing high-output power [9], [10]. There are three types of multi-level inverters as given: diode clamped multi-level inverter, flying capacitors multi-level inverter, and cascaded type multi-level inverter.

# 2.3. Cascaded H-bridge multi-level inverter

Initially, the CHBMLI topology was introduced for motor drive applications. Due to electronic switch power ratings, conventional converters lost power and were inefficient in high-voltage situations. CHBMLI offers lower costs and reduced electromagnetic interference compared to conventional converters [11]. Higher performance with low THD and increased efficiency are obtained. The requirement of separate, equal-value DC sources for each H-bridge in the symmetrical CHBMLI framework reduces the complexity of integrating various renewable energy sources [12]. The relationship between the number of H-bridges (n) and the leveled output per phase (m) is given by the equation m = 2n + 1. System requirements, applications, switch limits, and system losses should be considered while choosing the optimum number of levels [13].

# 2.4. Pulse width modulation (PWM) techniques

PWM transmits information through pulses, with data encoded in the pulse widths. To produce the desired result, PWM techniques are essential. There have been several modulation techniques proposed and discussed in the literature to accomplish this, including space vector PWM (SVPWM), selective harmonic elimination PWM (SHE-PWM), and multi-carrier PWM (MCPWM) [14].

# 2.4.1. Multi-carrier PWM scheme

Among the various modulation techniques, MCPWM is commonly used for controlling MLIs due to its simplicity. Techniques such as SPWM and SVPWM generate pulses that control the switches in MLIs, with the goal of producing a near-sinusoidal output voltage while minimizing harmonic distortion [15]. MCPWM, the most commonly used, simplifies pulse generation by comparing reference signals with triangular signals to control individual power switches. MCPWM requires (n-1) carrier waves for an n-level inverter [16]. It can be categorized into two types: level-shifted pulse width modulation (LSPWM) and

phase-shifted pulse width modulation (PSPWM). LSPWM encompasses various variants, including phase disposition-pulse width modulation (PD-PWM), phase opposition disposition-pulse width modulation (POD-PWM), alternate phase opposition disposition-pulse width modulation (APOD-PWM), and carrier-overlapping pulse width modulation (CO-PWM) [17]-[20].

## 2.4.2. Sinusoidal PWM

In SPWM, the comparison is performed between a sinusoidal modulating waveform and a triangular carrier waveform to determine the ON/OFF states of the switches. If the modulating wave is greater than the carrier wave, the switch is ON and the state is high. Lower amplitudes indicate low states and turn OFF the switch [21]. The THD in the output voltage can be reduced by controlling the inverter's switching pattern with SPWM. It can easily eliminate lower harmonics. In the case of the multi-carrier SPWM technique, (m-1) carrier waves are needed for an m-level CHBMLI. Maintaining uniform amplitude and frequency for all carrier waves or triangular waves is crucial.

# 2.4.3. Level shift PWM

This approach uses triangular waveforms for all carrier signals over the converter's voltage range. These signals have the same frequency and amplitude [22]. They are categorized based on the organization of carrier signals. Producing n levels requires (n-1) carrier signals. It is employed for inverter control without incorporating power balancing.

### 3. METHOD

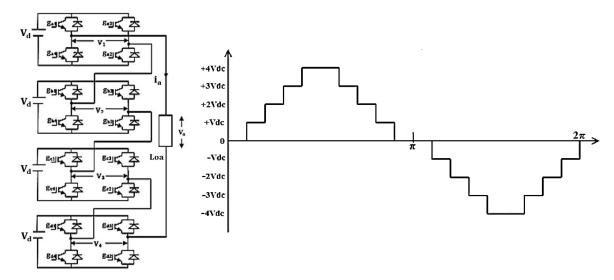

# 3.1. Simulation of cascaded H-bridge 7-level MLI

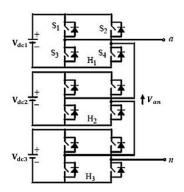

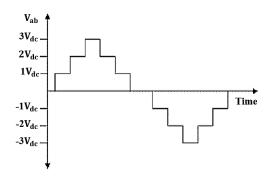

The circuit topology of the 7-level CHBMLI and the associated output voltage waveform are presented in Figures 2 and 3. It consists of three H-bridges, with each individual bridge consisting of four switches powered by a DC source. Each H-bridge is capable of generating a positive, negative, and zero voltage. In this topology, all three bridges are interconnected in series with each other [23], [24]. The voltage produced by each bridge is added together to get the required voltage. The voltage levels produced in this MLI are  $+3~V_{DC}$ ,  $+2~V_{DC}$ ,  $+2~V_$

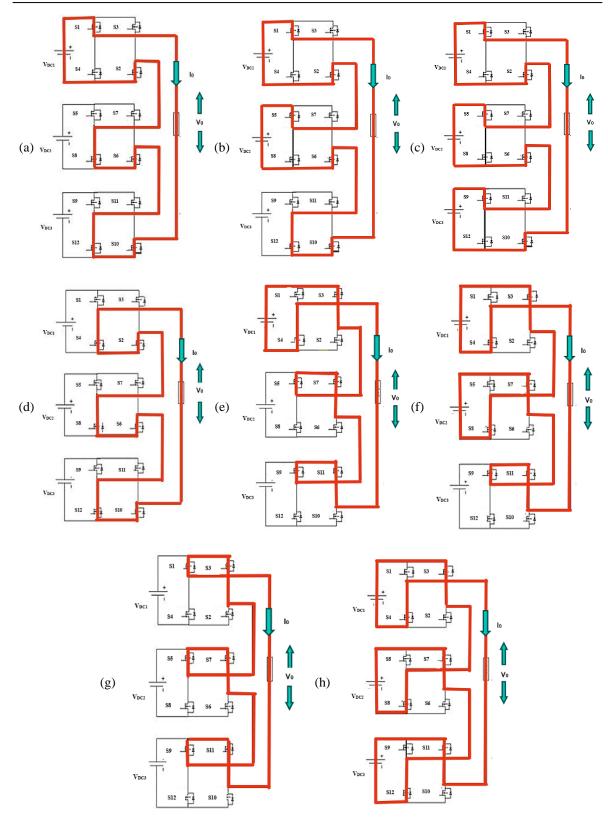

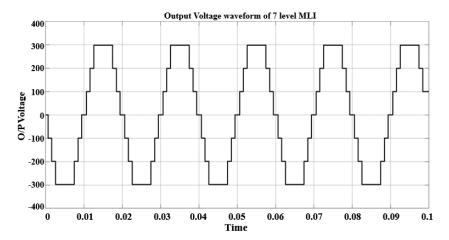

Switching operations that are used to generate the different voltages are given in Figure 4. In MLIs, corresponding voltages are generated when switches are toggled ON and OFF according to a set pattern, where 1 indicates the switch is ON and 0 indicates it is OFF [26]. Figures 5(a)-5(h) represent various working modes of the 7-level multi-level inverter through which various levels of voltages are produced. Figure 6 illustrates the output voltage waveform of a 7-level CHBMLI.

Figure 2. 7-level CHBMLI circuit topology

Figure 3. 7-level CHBMLI output voltage waveform

| $V_{DC}$ | $S_1$ | $S_2$ | S <sub>3</sub> | S <sub>4</sub> | $S_5$ | $S_6$ | $S_7$ | S <sub>8</sub> | S9 | S <sub>10</sub> | S <sub>11</sub> | S <sub>12</sub> |

|----------|-------|-------|----------------|----------------|-------|-------|-------|----------------|----|-----------------|-----------------|-----------------|

| +3       | 1     | 1     | 0              | 0              | 1     | 1     | 0     | 0              | 1  | 1               | 0               | 0               |

| +2       | 1     | 1     | 0              | 0              | 1     | 1     | 0     | 0              | 0  | 1               | 0               | 1               |

| +1       | 1     | 1     | 0              | 0              | 0     | 1     | 0     | 1              | 0  | 1               | 0               | 1               |

| 0        | 0     | 1     | 0              | 1              | 0     | 1     | 0     | 1              | 0  | 1               | 0               | 1               |

| U        | 1     | 0     | 1              | 0              | 1     | 0     | 1     | 0              | 1  | 0               | 1               | 0               |

| -1       | 0     | 0     | 1              | 1              | 1     | 0     | 1     | 0              | 1  | 0               | 1               | 0               |

| -2       | 0     | 0     | 1              | 1              | 0     | 0     | 1     | 1              | 1  | 0               | 1               | 0               |

| -3       | 0     | 0     | 1              | 1              | 0     | 0     | 1     | 1              | 0  | 0               | 1               | 1               |

Figure 4. Switching frequency of 7-level CHBMLI

$\label{eq:figure 5} Figure 5. Working modes of the 7-level multi-level inverter: (a) $V_{dc}$, (b) 2 $V_{dc}$, (c) 3 $V_{dc}$, (d) 0 $V_{dc}$, (e) -V_{dc}$, (f) -2 $V_{dc}$, (g) -3 $V_{dc}$, and (h) 0 $V_{dc}$.}$

Figure 6. 7-level CHBMLI output voltage waveform

## 3.2. Simulation of cascaded H-bridge 9-level MLI

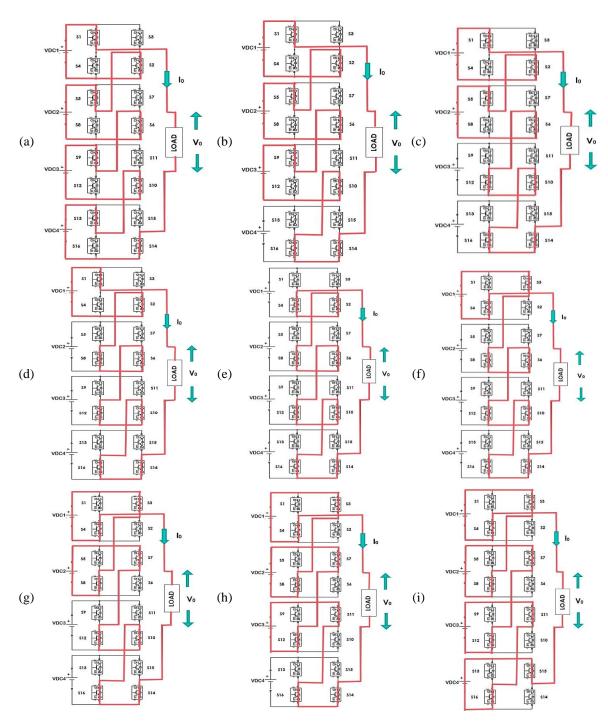

The 9-level CHBMLI is a specific configuration that offers advantages in power conversion applications. It consists of four H-bridges, each composed of four switches, generating multiple voltage levels, including positive, negative, and zero voltages. By combining these voltage levels, it achieves higher resolution and flexibility in generating the output voltage waveform [27]. This configuration enhances the quality of the output waveform by decreasing harmonic content, hence minimizing noise and distortion. It also provides reduced switching losses and improved efficiency. The 9-level CHBMLI's high voltage resolution is advantageous for applications that demand precise voltage control, enabling more exact adjustments in output voltage and enhancing control and accuracy in different industrial processes [28].

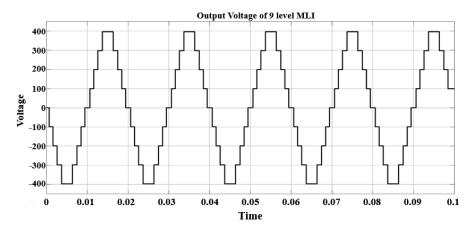

The general structure of the 9-level CHBMLI and its corresponding waveform are shown in Figures 7 and 8. It produces an output waveform of four positive levels, four negative levels, and a zero level. There are 9 switching modes and it generates the required levels of output of voltages which are  $+4~V_{DC}$ ,  $+3~V_{DC}$ ,  $+2~V_{DC}$ ,  $+V_{DC}$ , 0,  $-V_{DC}$ ,  $-2~V_{DC}$ ,  $-3~V_{DC}$ , and  $-4~V_{DC}$ . Figure 9 indicates the corresponding voltages according to the switching pattern. Figures 10(a)-10(i) represent various working modes of the 9-level CHBMLI through which various levels of voltages are produced [29]. Figure 11 represents the output voltage waveform of a 9-level CHBMLI.

Figure 7. 9-level CHBMLI circuit topology

Figure 8. 9-level CHBMLI output voltage waveform

| V <sub>DC</sub> | S <sub>1</sub> | S <sub>2</sub> | S <sub>3</sub> | S <sub>4</sub> | Ss | S <sub>6</sub> | S <sub>7</sub> | S <sub>8</sub> | S <sub>9</sub> | S <sub>10</sub> | S <sub>11</sub> | S <sub>12</sub> | S <sub>13</sub> | S <sub>14</sub> | S <sub>15</sub> | S <sub>16</sub> |

|-----------------|----------------|----------------|----------------|----------------|----|----------------|----------------|----------------|----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| 4               | 1              | 1              | 0              | 0              | 1  | 1              | 0              | 0              | 1              | 1               | 0               | 0               | 1               | 1               | 0               | 0               |

| 3               | 1              | 1              | 0              | 0              | 1  | 1              | 0              | 0              | 1              | 1               | 0               | 0               | 0               | 1               | 0               | 1               |

| 2               | 1              | 1              | 0              | 0              | 1  | 1              | 0              | 0              | 0              | 1               | 0               | 1               | 0               | 1               | 0               | 1               |

| 1               | 1              | 1              | 0              | 0              | 0  | 1              | 0              | 1              | 0              | 1               | 0               | 1               | 0               | 1               | 0               | 1               |

| 0               | 0              | 1              | 0              | 1              | 0  | 1              | 0              | 1              | 0              | 1               | 0               | 1               | 0               | 1               | 0               | 1               |

| -1              | 0              | 0              | 1              | 1              | 0  | 1              | 0              | 1              | 0              | 1               | 0               | 1               | 0               | 1               | 0               | 1               |

| -2              | 0              | 0              | 1              | 1              | 0  | 0              | 1              | 1              | 0              | 1               | 0               | 1               | 0               | 1               | 0               | 1               |

| -3              | 0              | 0              | 1              | 1              | 0  | 0              | 1              | 1              | 0              | 0               | 1               | 1               | 0               | 1               | 0               | 1               |

| -4              | 0              | 0              | 1              | 1              | 0  | 0              | 1              | 1              | 0              | 0               | 1               | 1               | 0               | 0               | 1               | 1               |

Figure 9. Switching frequency of 9-level CHBMLI

$\label{eq:figure 10.} Figure 10. Working modes of the 9-level CHBMLI: (a) 4 V_{dc}, (b) 3 V_{dc}, (c) 2 V_{dc}, (d) V_{dc}, (e) 0 V_{dc}, (f) - V_{dc}, \\ (g) -2 V_{dc}, (h) -3 V_{dc}, and (i) -4 V_{dc}$

Figure 11. 9-level CHBMLI output voltage waveform

# 3.3. THD analysis

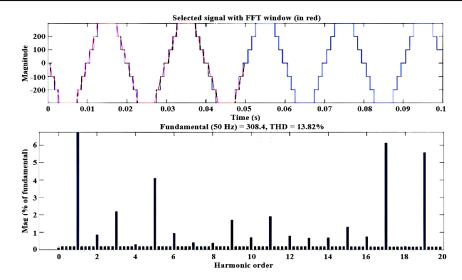

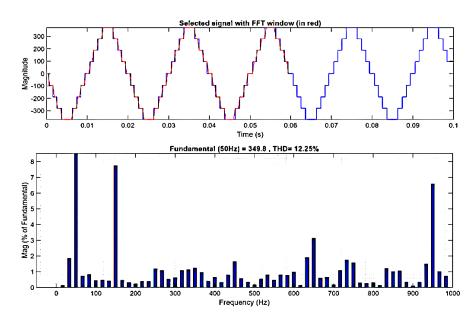

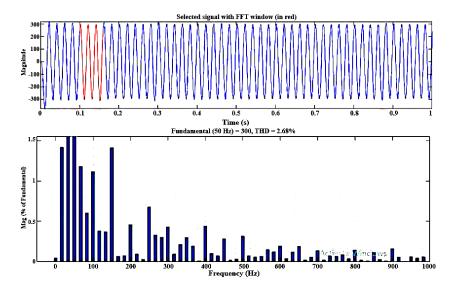

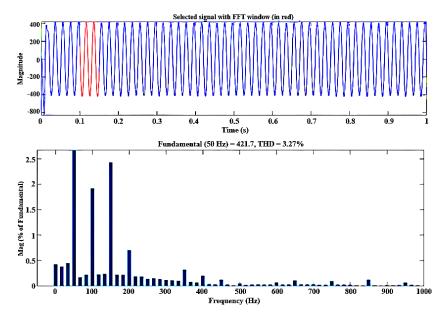

The quality of a waveform is measured by total harmonic distortion (THD), which is defined by the harmonic number (n). Harmonics in the system can cause equipment degradation and it is crucial to minimize them. In the context of the MLI, controlled switching pulses in the output voltage ( $V_{out}$ ) are used to reduce the THD. Lowering THD helps eliminate the presence of harmonics and improves the quality of power delivered [30]. Harmonic distortions primarily stem from the usage of non-linear loads, particularly those incorporating power electronics, as these loads do not draw current in a sinusoidal manner. IEEE Standards typically define limit values for voltage harmonics, with a THD limit of 5% and a limit of 3% for each individual harmonic. DC voltages and inverter commutation angles affect output voltage THD. In an ideal scenario with cascaded symmetrical inverters, all DC sources remain constant and equal, as in (1). The THD analysis of the 7-level and 9-level CHBMLI model is shown in Figures 12 and 13, respectively.

the

$$THD_V = \frac{\sqrt{\sum_{n=2}^{\infty} (v_{n,RMS})^2}}{v_{1,RMS}} = \frac{\sqrt{\sum_{n=2}^{\infty} (v_{RMS})^2 - (v_{1,RMS})^2}}{v_{1,RMS}}$$

(1)

## 3.4. Design and implementation of a passive filter

Due to the switching nature of MLIs, it introduces undesired harmonics and distorts the AC output waveform. Filters are utilized to mitigate the harmonics and enhance fundamental components of the output voltage. Filters allow for a smoother and more sinusoidal waveform, thus reducing harmonic distortion. There are three main types of filters commonly used, they are inductor filter (L), inductor-capacitor filter (LC), and inductor-capacitor-inductor filter (LCL). The LC filter, also known as a passive LC filter or second-order filter, is an electronic circuit that utilizes inductors (L) and capacitors (C) to shape or filter the frequency response of a signal. It is designed to meet IEEE standards by achieving less than a 5% deviation. The LC filter incorporates both an inductor and a capacitor, making it a second-order filter. In the LC filter, a capacitor is connected to the grid in parallel. Applied with a switching method, the LC filter is capable of removing lower-order odd harmonics from the output. For single-phase full bridge inverters,  $V_{out}(rms) = V_{DC}$ ,  $V = 100\sqrt{2}$  sin wt,  $\Delta I_L = 20\%$  of the rated current, and  $\Delta I_{Lmax} = \frac{V_{dC}}{4 \times L \times F_{SW}}$ .

$$L = \frac{V_{dc}}{4 \times \Delta_{I_{L} max} \times F_{SW}} \tag{2}$$

$$C = \left(\frac{10}{2 \times \Pi \times F_{SW}}\right)^2 \times \frac{1}{L} \tag{3}$$

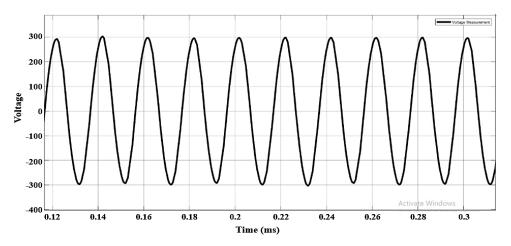

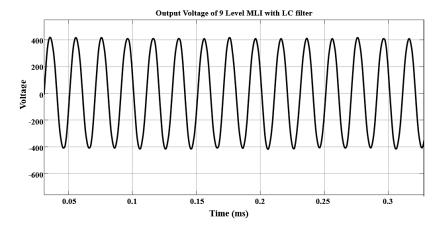

Where L is inductance in mH,  $F_{sw}$  is switching frequency in Hz, and C is the capacitance in mF. Figures 14 and 15 represent the output voltage waveforms of a 7-level and 9-level CHBMLI with a passive LC filter. Figures 16 and 17 represent the THD analysis of a 7-level, 9-level CHBMLI with a filter. The observations from the above models are tabulated in Table 1.

Figure 12. THD analysis of 7-level CHBMLI

Figure 13. THD analysis of 9-level CHBMLI

Figure 14. Output voltage waveform of 7-level CHBMLI with an LC filter

Figure 15. Output voltage waveform of 9-level CHBMLI with an LC filter

Figure 16. THD analysis of 7-level CHBMLI with passive LC filter

Figure 17. THD analysis of 9-level CHBMLI with passive LC filter

Table 1. THD comparison of 7-level and 9-level MLI

|              | Tuote 1. 111D comp         | arison or , | iever and a rever ivida                     |

|--------------|----------------------------|-------------|---------------------------------------------|

| Level of MLI | Parameters                 | THD value   | Fundamental component of output voltage (V) |

| 7-level MLI  | Fixed DC without LC filter | 13.82%      | 308.4                                       |

|              | Fixed DC with LC filter    | 2.68%       | 300                                         |

| 9-level MLI  | Fixed DC without LC filter | 12.25%      | 349.8                                       |

|              | Fixed DC with LC filter    | 3.27%       | 421.7                                       |

## 4. CONCLUSION

The CHBMLI is capable of producing superior quality output waveforms compared to traditional two-level inverters, which has contributed to its rising popularity in applications requiring medium to high power. When it comes to MLI, PWM techniques are necessary to achieve the desired output. It was decided to use the level shift pulse width modulation (PWM) technique for this project, with a sine wave serving as the modulating signal. The total harmonic distortion (THD) was measured to be 13.82% for the 7-level inverter and 12.25% for the 9-level inverter, respectively. It is evident that increasing the number of levels in the MLI lowers the THD percentage and enhances the fundamental voltage, which signifies improved inverter performance. The efficiency of passive filters in lowering THD is another key takeaway from this effort. Through the execution of the required computations, an LC filter was designed. The THD values for 7-level and 9-level CHBMLIs are reported to be 2.68% and 3.27%, respectively, once the passive filter that was constructed is incorporated with the proper DC input voltage. Precise adjustment of filters is necessary to generate pure sinusoidal waveforms of voltage and current, which will decrease THD and enhance efficiency.

# **ACKNOWLEDGEMENTS**

This research work was supported by "Woosong University's Academic Research Funding - 2024".

## REFERENCES

- [1] C. R. Balamurugan and R. Besnraj, "Analysis of various carriers overlapping PWM strategies for a single-phase ternary multilevel inverter," *International Journal of Applied Power Engineering (IJAPE)*, vol. 7, no. 1, pp. 27–39, 2018, doi: 10.11591/ijape.v7.i1.pp27-39.

- [2] T. P. Sanu and A. Xavier, "Cascaded H bridge fifteen level inverter," *International Journal of Engineering Research & Technology (IJERT)*, vol. 4, no. 9, pp. 880–883, 2015, [Online]. Available: https://www.ijert.org/research/cascaded-h-bridge-fifteen-level-inverter-IJERTV4IS090848.pdf

- [3] P. R. Bana, K. P. Panda, and G. Panda, "Power quality performance evaluation of multilevel inverter with reduced switching devices and minimum standing voltage," *IEEE Transactions on Industrial Informatics*, vol. 16, no. 8, pp. 5009–5022, 2020, doi: 10.1109/TII.2019.2953071.

- [4] V. T. Ha, P. T. Giang, and P. Vu, "Multilevel inverter application for railway traction motor control," *Bulletin of Electrical Engineering and Informatics*, vol. 11, no. 4, pp. 1855–1866, 2022, doi: 10.11591/eei.v11i4.3964.

- [5] D. Karthikeyan et al., "PI controller for photovoltaic-fed novel multilevel inverter topologies," *Indonesian Journal of Electrical Engineering and Computer Science*, vol. 29, no. 3, pp. 1268–1280, 2023, doi: 10.11591/ijeecs.v29.i3.pp1268-1280.

- [6] A. T. Balakrishnan, A. James, J. T. Job, and A. Thomas, "Seven level inverter," *International Journal of Engineering Research & Technology (IJERT)*, vol. 6, no. 4, pp. 857–876, 2017, doi: 10.17577/IJERTV6IS040653.

- [7] T. Qanbari and B. Tousi, "Single-source three-phase multilevel inverter assembled by three-phase two-level inverter and two single-phase cascaded h-bridge inverters," *IEEE Transactions on Power Electronics*, vol. 36, no. 5, pp. 5204–5212, 2021, doi: 10.1109/TPEL.2020.3029870.

- [8] G. Grandi, J. Loncarski, and O. Dordevic, "Analysis and comparison of peak-to-peak current ripple in two-level and multilevel PWM inverters," *IEEE Transactions on Industrial Electronics*, vol. 62, no. 5, pp. 2721–2730, 2015, doi: 10.1109/TIE.2014.2363624.

- [9] N. Bhargava, S. Gupta, and S. P. Phulambrikar, "Analysis of asymmetrical cascaded 7 level and 9 level multilevel inverter design for asynchronous motor," *International Journal of Engineering Research & Technology (IJERT)*, vol. 3, no. 8, pp. 499–504, 2014, doi: 10.17577/IJERTV3IS080450.

- [10] N. Ramalingam and A. Thiagarajan, "FPGA-based fault analysis for 7-level switched ladder multi-level inverter using decision tree algorithm," *International Journal of Reconfigurable and Embedded Systems (IJRES)*, vol. 12, no. 2, pp. 157–164, 2023, doi: 10.11591/ijres.v12.i2.pp157-164.

- [11] A. Gaikwad and P. A. Arbune, "Study of cascaded H-Bridge multilevel inverter," in 2016 International Conference on Automatic Control and Dynamic Optimization Techniques (ICACDOT), Pune, India, 2016, pp. 179–182, doi: 10.1109/ICACDOT.2016.7877574.

- [12] S. M and A. K. Parvathy, "Improved reliable multilevel inverter for renewable energy systems," *Indonesian Journal of Electrical Engineering and Computer Science*, vol. 14, no. 3, pp. 1141–1147, 2019, doi: 10.11591/ijeecs.v14.i3.pp1141-1147.

- [13] H. V Sabhaya and V. S. Sheth, "Comparative analysis of cascade H-bridge multilevel voltage source inverter," *International Journal of Electronics, Electrical and Computational System (IJEECS)*, vol. 4, pp. 168–178, 2015.

- [14] B. P. McGrath and D. G. Holmes, "Multicarrier PWM strategies for multilevel inverters," IEEE Transactions on Industrial Electronics, vol. 49, no. 4, pp. 858–867, 2002, doi: 10.1109/TIE.2002.801073.

- [15] P. Kiruthika and R. Kannan, "Multi-carrier based 27-level hybrid multi-level inverter interface with photovoltaic," TELKOMNIKA Indonesian Journal of Electrical Engineering, vol. 13, no. 3, pp. 467–475, 2015, doi: 10.11591/telkomnika.v13i3.7140.

- [16] M. Manjrekar and G. Venkataramanan, "Advanced topologies and modulation strategies for multilevel inverters," in PESC Record. 27th Annual IEEE Power Electronics Specialists Conference, Baveno, Italy, 1996, pp. 1013–1018, doi: 10.1109/PESC.1996.548706.

- [17] T. Kaliannan, J. R. Albert, D. M. Begam, and P. Madhumathi, "Power quality improvement in modular multilevel inverter using for different multicarrier PWM," *European Journal of Electrical Engineering and Computer Science*, vol. 5, no. 2, pp. 19–27, 2021, doi: 10.24018/ejece.2021.5.2.315.

- [18] B. G. Shivaleelavathi, C. Srikanth, and V. Yatnalli, "Review on multi level inverter topologies and control strategies for solar power conversion," *International Journal of Engineering Technology*, vol. 8, no. 2, pp. 295–315, 2020, doi: 10.24003/emitter.v8i2.500.

- [19] H. Chadli, S. Chadli, M. Boutouba, M. Saber, and A. Tahani, "Hardware implementation and performance evaluation of microcontroller-based 7-level inverter using POD-SPWM technique," *Indonesian Journal of Electrical Engineering and Computer Science*, vol. 23, no. 1, pp. 120–131, 2021, doi: 10.11591/ijeecs.v23.i1.pp120-131.

- [20] M. Venkateswarlu, G. Satheesh, and P. Sujatha, "Modified SPWM technique for single-phase variable voltage nine level inverter for PV system," *International Journal of Power Electronics and Drive Systems (IJPEDS)*, vol. 14, no. 4, pp. 2173–2182, 2023, doi: 10.11591/ijpeds.v14.i4.pp2173-2182.

- [21] P. H. Zope, P. G. Bhangale, P. Sonare, and S. R. Suralkar, "Design and implementation of carrier-based Sinusoidal PWM inverter," *International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering*, vol. 1, no. 4, pp. 230–236, 2012.

- [22] S. Rahman, M. Meraj, A. Iqbal, B. P. Reddy, and I. Khan, "A combinational level-shifted and phase-shifted PWM technique for symmetrical power distribution in CHB inverters," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 11, no. 1, pp. 932–941, 2023, doi: 10.1109/JESTPE.2021.3103610.

- [23] T. Abhilash, K. Annamalai, and S. V. Tirumala, "A seven-level VSI with a front-end cascaded three-level inverter and flying-capacitor-fed H-bridge," *IEEE Transactions on Industry Applications*, vol. 55, no. 6, pp. 6073–6088, 2019, doi: 10.1109/TIA.2019.2933378.

- [24] M. K. Das, K. C. Jana, and A. Sinha, "Performance evaluation of an asymmetrical reduced switched multi-level inverter for a grid-connected PV system," *IET Renewable Power Generation*, vol. 12, no. 2, pp. 252–263, 2017, doi: 10.1049/iet-rpg.2016.0895.

- [25] C. I. Odeh, A. Lewicki, and M. Morawiec, "A single-carrier-based pulse-width modulation template for cascaded H-bridge multilevel inverters," *IEEE Access*, vol. 9, pp. 42182–42191, 2021, doi: 10.1109/ACCESS.2021.3065743.

- [26] A A. Vinothkumar, S. Selvakumar, and M. Vigneshkumar, "Modelling and analysis of photo voltaic cell fed seven level multi-string inverter," *International Journal of Engineering Research & Technology (IJERT)*, vol. 3, no. 2, pp. 1417–1422, 2014.

- [27] A. A. Al-Samawi and H. Trabelsi, "New nine-level cascade multilevel inverter with a minimum number of switches for PV systems," *Energies*, vol. 15, no. 16, p. 5867, 2022, doi: 10.3390/en15165857.

- [28] P. S. Kumar, S. P. Natarajan, A. Nachiappan, and B. Shanthi, "Performance evaluation of nine level modified CHB multilevel inverter for various PWM strategies," *International Journal of Modern Engineering Research (IJMER)*, vol. 3, no. 5, pp. 2758– 2766, 2013.

- [29] K. K. Gupta and S. Jain, "A novel multilevel inverter based on switched DC sources," *IEEE Transactions on Industrial Electronics*, vol. 61, no. 7, pp. 3269–3278, 2014, doi: 10.1109/TIE.2013.2282606.

- [30] T. G. Habetler, R. Naik, and T. A. Nondahl, "Design and implementation of an inverter output LC filter used for dv/dt reduction," IEEE Transactions on Power Electronics, vol. 17, no. 3, pp. 327–331, 2002, doi: 10.1109/TPEL.2002.1004240.

# **BIOGRAPHIES OF AUTHORS**

Chava Sunil Kumar has a B.Tech. degree in electrical and electronics engineering in the year 2000 and M.Tech. degree in electrical power engineering the year 2006 from JNTU College of Engineering, Kukatpally, Hyderabad, AP, India and Ph.D. from JNTUH University Hyderabad, TS, India in 2013. He has 23 years of teaching experience. Presently, he is working as a professor in the Department of Electrical and Electronics Engineering at BVRIT HYDERABAD College of Engineering for Women, Hyderabad, Telangana, India since 2013. His area of interest includes electrical power systems, power electronics, and electrical machines. He can be contacted at email: sunilkumar.ch@bvrithyderabad.edu.in.

Surender Reddy Salkuti received a Ph.D. degree in electrical engineering from the Indian Institute of Technology, New Delhi, India, in 2013. He was a postdoctoral researcher at Howard University, Washington, DC, USA, from 2013 to 2014. He is currently an associate professor with the Department of Railroad and Electrical Engineering, at Woosong University, Daejeon, South Korea. His current research interests include market clearing, including renewable energy sources, demand response, and smart grid development with the integration of wind, and solar photovoltaic energy sources. He can be contacted at email: surender@wsu.ac.kr.

Sai Sruthi Bhupathiraju © scompleted her B.Tech. in electrical and electronics engineering from BVRIT HYDERABAD College of Engineering for Women, Nizampet, Hyderabad, Telangana. Her areas of interest include power system applications and power electronic converters. She can be contacted at email: sruthibhupathiraju27@gmail.com.

Kasoju Pragathi Balakishan completed her B.Tech. in electrical and electronics engineering from BVRIT HYDERABAD College of Engineering for Women, Nizampet, Hyderabad, Telangana. Her areas of interest are power system applications and power electronic converters. She can be contacted at email: pragathi.kasoju01@gmail.com.

Paipoti Pooja Chaturya (D) (S) (C) completed her B.Tech. in electrical and electronics engineering from BVRIT HYDERABAD College of Engineering for Women, Nizampet, Hyderabad, Telangana. Her areas of interest are power system applications and power electronic converters. She can be contacted at email: chaturyapaipoti@gmail.com.

**Rishitha Namineni** completed her B.Tech. in electrical and electronics engineering from BVRIT HYDERABAD College of Engineering for Women, Nizampet, Hyderabad, Telangana. Her areas of interest are power system applications and power electronic converters. She can be contacted at email: namanirishital@gmail.com.